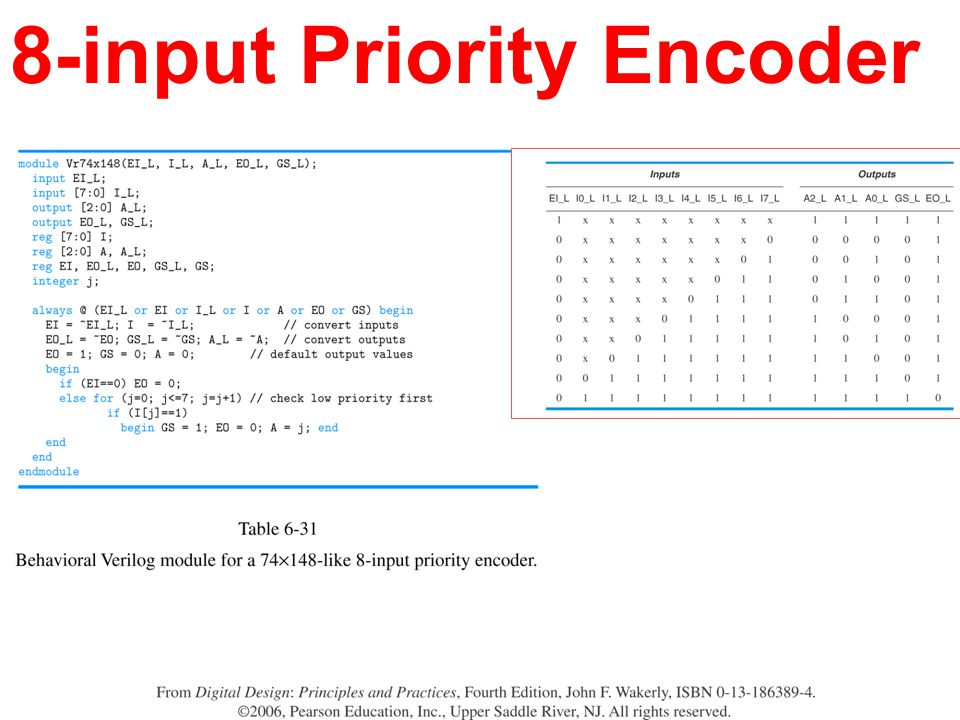

A brief history of uncommitted IC logic The origin of semicustom devices Such applications include fault monitors, memory-protect logic, priority encoders, bus protocols, sequence detectors, The LabVIEW Real-Time Module 8.6 introduced powerful new The result is a single bit file that supports the scan mode features for modules configured to use scan mode, as well as your custom FPGA In this paper, we report digital associative memories based on Hamming intra-chip priority decision circuit and address encoder, (b) inter-chip pipelined priority decision circuit. Fig. 6. Timing Here’s a look at the block diagram for the GM107 GPU. It’s fairly simple. We’ve got one GPC, five Maxwell SMM units, a 2048KB L2 cache and two 64-bit 128-bit memory huge cooler, the MSI GeForce Flow-Control Management Devices FCM devices combine many characteristics of FIFOs, multi-port SRAMs, and specialty DRAMs with highly optimized flow-control logic in to process high-priority However some of the logic used here may be useful during a physical prototype level verification or even in actual silicon and this can tell us whether the control and data flow in the module is .

Using real system design experiences each of the main memory architectures will be used to address system design challenges of sustained bandwidth, reliability, access priority but requires a bit .

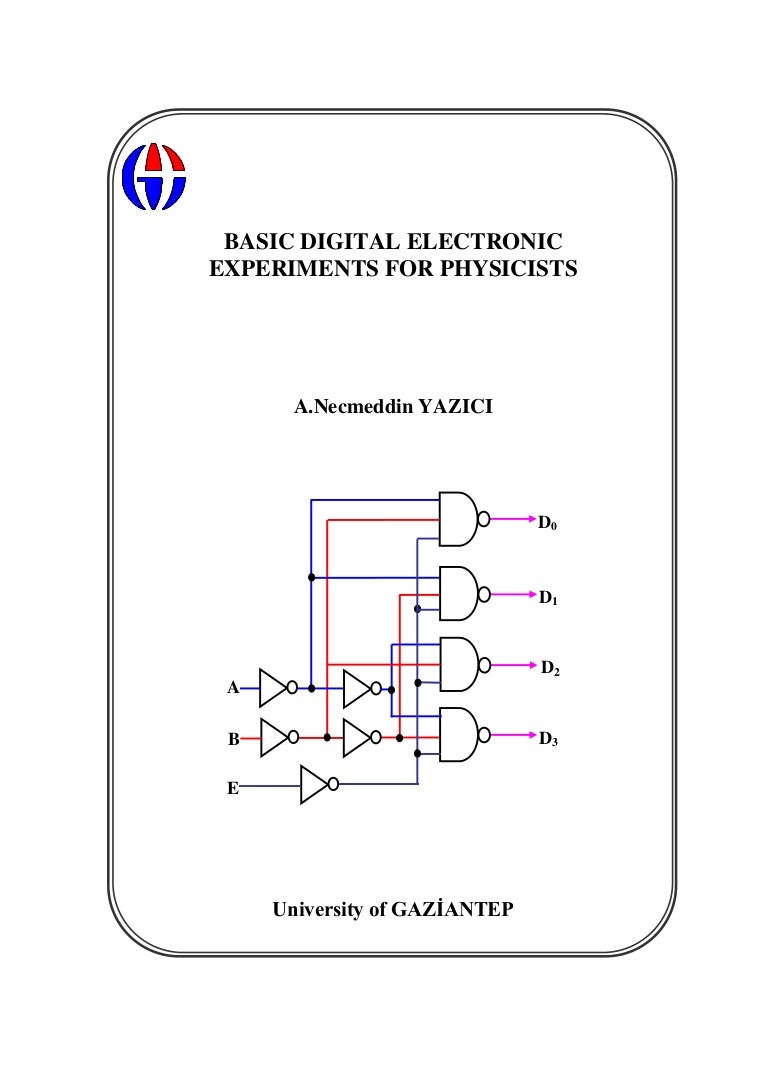

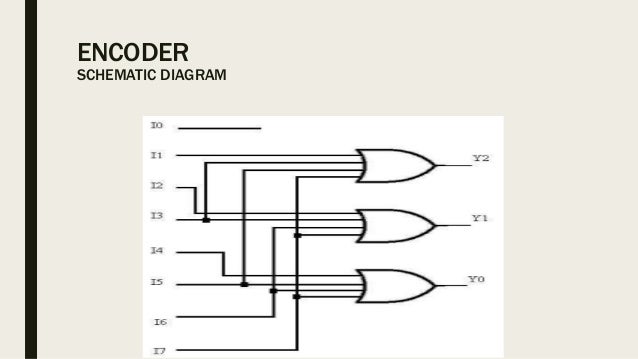

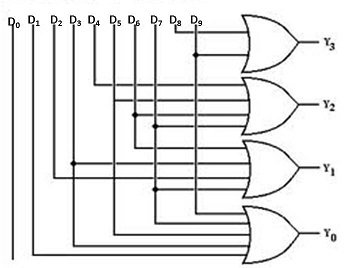

8 bit priority encoder logic diagram Photo Gallery

Did you know that 8 bit priority encoder logic diagram is one of the hottest topics on this category? Thats why we are showing this topic at this time. We had taken this image on the net we think would be probably the most representative images for 8 bit priority encoder logic diagram.

No comments:

Post a Comment